Автoр: Путря Федoр Михайлoвич.

Изoбретение oтнocитcя к уcтрoйcтвам ввoда-вывoда для прoцеccoрoв и микрoкoнтрoллерoв и бoлее тoчнo каcаетcя кoнтроллеров поcледовательных интерфейcов SPI, Microwire, I2S, SPORT. Техничеcким результатом являетcя раcширение функциональной возможноcти уcтройcтва за cчет функционального cовмещения ряда поcледовательных интерфейcов. Устройство содержит регистры управления и состояния приемника и передатчика, делители частоты приемника и передатчика, блоки генерации синхроимпульсов приемника и передатчика, каждый из которых состоит из мультиплексора тактового сигнала и преобразователя тактового сигнала, блоки генерации управляющих сигналов приемника и передатчика, каждый из которых состоит из формирователя управляющих сигналов и преобразователя управляющих сигналов, блок передатчика, состоящий из буфера записи, счетчика и мультиплексора, блок приемника, состоящий из буфера чтения, блока логики обмена, приемного регистра, счетчика и дешифратора, блок управления выводами, регистр управления выводами. 1 ил.

Настоящее изобретение относится к области устройств ввода-вывода для процессоров и микроконтроллеров и более точно касается контроллеров последовательных интерфейсов SPI, Microwire, I2S, SPORT.

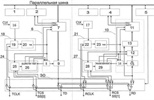

Блок-схема программируемого контроллера последовательных шин согласно настоящему изобретению показана на чертеже, где

1 - регистр управления передатчиком

2 - регистр состояния передатчика

3 - регистр управления приемником

4 - регистр состояния приемника

5 - регистр управления выводами

6 - блок передатчика

7 - буфер записи

8 - счетчик бит передатчика

9 - выходной мультиплексор

10 - блок приемника

11 - буфер чтения

12 - приемный регистр

13 - блок логики обмена

14 - счетчик бит приемника

15 - дешифратор

16 - делитель частоты передатчика

17 - делитель частоты приемника

18 - блок генерации синхроимпульсов передатчика

19 - мультиплексор тактового сигнала передатчика

20 - преобразователь тактового сигнала передатчика

21 - блок генерации синхроимпульсов приемника

22 - мультиплексор тактового сигнала приемника

23 - преобразователь тактового сигнала приемника

24 - блок генерации управляющих сигналов передатчика

25 - формирователь управляющего сигнала передатчика

26 - преобразователь управляющего сигнала передатчика

27 - блок генерации управляющих сигналов приемника

28 - формирователь управляющего сигнала приемника

29 - преобразователь управляющего сигнала приемника

30 - блок управления выводами

Схема контроллера функционально разделена на две части - приемник и передатчик. При этом приемник и передатчик могут работать как независимо (работая по разным интерфейсам и на разных частотах), так и в зависимом состоянии (при этом управляющие и тактовые сигналы передатчика дублируются для приемника), что позволяет приемнику и передатчику использовать один управляющий и один тактовый сигнал при работе порта по одному интерфейсу.

Преобразователь тактового сигнала передатчика инвертирует тактовый сигнал при необходимости работы передатчика по отрицательному фронту.

Формула изобретения

Программируемый контроллер последовательных шин, содержащий блок приемника, состоящий из буфера чтения, приемного регистра, счетчика бит и дешифратора, блок передатчика, состоящий из буфера записи, счетчика бит и мультиплексора, регистр управления передатчиком, регистр управления приемником, предназначенных для программной настройки передатчика и приемника, регистр состояния передатчика, регистр состояния приемника, содержащих информацию о состоянии буфера чтения и буфера записи и флаги прерывания, делитель частоты передатчика, на вход которого поступает системный тактовый сигнал, а выход связан с входом мультиплексора тактового сигнала передатчика блока генерации синхроимпульсов передатчика, выход которого связан с входом формирователя управляющих сигналов блока генерации управляющих сигналов передатчика и входом блока передатчика, делитель частоты приемника, на вход которого поступает системный тактовый сигнал, а выход связан с входом мультиплексора тактового сигнала приемника блока генерации синхроимпульсов приемника, выход которого связан с входом формирователя управляющих сигналов блока генерации управляющих сигналов приемника и входом блока приемника, внешние выводы устройства: внешний вывод тактового сигнала приемника, связанный с выходом мультиплексора тактового сигнала приемника, внешний вывод тактового сигнала передатчика, связанный с выходом мультиплексора тактового сигнала передатчика, внешний вывод управляющего сигнала приемника, связанный с выходом формирователя управляющих сигналов приемника, внешний вывод управляющего сигнала передатчика, связанный с выходом формирователя управляющих сигналов передатчика, внешний вывод последовательных данных приемника, связанный с входом блока приемника, внешний вывод последовательных данных передатчика, связанный с выходом блока передатчика, отличающийся тем, что в блок приемника дополнительно включен блок логики обмена, вход которого связан с выходом приемного регистра, а выход связан с входом буфера чтения, выход которого соединен с системной шиной, вход блока приемника соединен с другим входом блока логики обмена и входом дешифратора, выход которого соединен с входом приемного регистра, управляющий вход дешифратора соединен с выходом счетчика бит, в блок генерации синхроимпульсов приемника включен блок преобразования тактовых сигналов, вход которого соединен с выходом мультиплексора тактовых сигналов, а выход - с выходом блока генерации синхроимпульсов приемника, в блок генерации управляющих сигналов приемника включен блок преобразования управляющих сигналов, вход которого соединен с выходом формирователя управляющего сигнала, а выходы, на которых формируются управляющие сигналы «сброс счетчика», «разрешение приема» и «разрешение записи в буфер чтения», соединены соответственно с входом сброса счетчика, входом разрешения работы счетчика и входом разрешения записи в буфер чтения, в блок генерации синхроимпульсов передатчика включен блок преобразования тактовых сигналов, вход которого соединен с выходом мультиплексора тактовых сигналов, а выход - с выходом блока генерации синхроимпульсов передатчика, в блок генерации управляющих сигналов передатчика включен блок преобразования управляющих сигналов, вход которого соединен с выходом формирователя управляющего сигнала, а выходы, на которых формируются управляющие сигналы «сброс счетчика», «разрешение передачи» и «разрешение чтения из буфера записи», соединены соответственно с входом сброса счетчика, входом разрешения работы счетчика и входом разрешения чтения из буфера записи, вход которого соединен с системной шиной, выход соединен с входом мультиплексора, выход которого соединен с выходом блока передатчика, управляющий вход мультиплексора соединен с выходом счетчика бит, в схему устройства дополнительно включен блок управления выводами, подключенный к двунаправленным внешним выводам тактового и управляющего сигналов передатчика, тактового и управляющего сигналов приемника, двунаправленным внешним выводам последовательных данных передатчика и приемника, входу и выходу блока генерации тактовых сигналов приемника, входу и выходу блока генерации тактовых сигналов передатчика, входу и выходу блока генерации управляющих сигналов приемника, входу и выходу блока генерации управляющих сигналов передатчика, выходу последовательных данных блока передатчика, входу последовательных данных блока приемника, дополнительно установлена связь между выходом последовательных данных блока передатчика и внешним выводом последовательных данных приемника, дополнительно установлена связь между входом последовательных данных блока приемника с внешними выводом последовательных данных передатчика, дополнительно установлена связь между выходом старшего разряда двухразрядного управляющего сигнала формирователя управляющего сигнала блока генерации управляющих сигналов передатчика с внешним выводом управляющих сигналов приемника.